ATE 디지털 시스템은 전통적으로 시퀀서, 포맷터, 타이밍 발생기 및 핀 전자 제품. 설계의 각 섹션에 사용할 구성 요소에 대한 결정은 주로 원하는 성능 사양과 비용에 따라 결정됩니다. 이러한 구성 요소는 개별 완전 맞춤형 ASIC, 현장 프로그래밍 가능 게이트 어레이 또는 상용 부품에 이르기까지 다양합니다.

FPGA (Field Programmable Gate Array)는 유연성을 제공하며 중저 성능 ATE 디지털 하위 시스템의 시퀀서 및 타이밍 / 포맷에 사용되었습니다.

FPGA로 시퀀서를 구현하면 로직, 메모리 또는 혼합 신호 테스트를 위해 디지털 서브 시스템을 맞춤화 할 수있는 유연성을 제공합니다. 필요한 FPGA 클로킹은 일반적으로 대상 FPGA의 사양 내에 있습니다. 시퀀서 및 패턴 실행 단계는 일반적으로 경쟁 제품과 비교하여 각 시스템을 고유하게 만드는 요소입니다.

형식 및 타이밍 기능은 일반적으로 서로 다른 ATE 플랫폼간에 유사합니다. 차이는 에지 배치 분해능 및 정확도를 순환하는주기와 채널 기울기 보정에 사용되는 미세 왜곡 제어에 있습니다. 미세 왜곡 보정 제어는 종종 핀 전자 IC에서 사용할 수 있습니다.

FPGA는 타이밍 및 포맷 기능에 성공적으로 사용되었지만 시스템 성능 요구 사항이 50-100Mhz 패턴 속도 이상으로 증가하고 시스템 에지 배치 정확도가 1ns 미만으로 떨어지면 FPGA가 빠르게 제한 요소가됩니다. FPGA I / O 구조의 SERDES 엔진은 <100ps 해상도를 제공 할 수 있지만, 에지 투 에지 타이밍 배치를 위해이 신뢰성을 구현하면 설계 시간이 늘어나고 설계자가 더 크고 값 비싼 FPGA를 선택하게됩니다.

SERDES 블록의 가장 일반적인 용도는 PCIe와 같은 다양한 통신 프로토콜에 사용되며 FPGA 설계 도구는 이러한 기능을 설계하고 특성화하는 데 탁월한 도구를 제공합니다. 설계자는 이러한 SERDES 블록을 사용하여 타이밍 섹션을 설계 할 때 종종 장애물에 부딪히며 문제를 해결하기 위해 FPGA 공급 업체에서 사용할 수있는 도구가 제한되어 있습니다. 설계자는 종종 이러한 타이밍 회로를 구현하고 특성화하기 위해 예산 엔지니어링 시간의 10 배를 소비합니다. 일반적인 문제에는 채널간에 일관되지 않은 선형성, 허용 가능한 지터보다 높은 지터, 실행간에 설계 라우팅의 어려움이 포함됩니다.

설계자가 채널 수를 늘리려 고 시도함에 따라 더 크고 값 비싼 FPGA로 마이그레이션해야합니다. 과거에는 설계자들이 더 빠르고 더 큰 FPGA를 저렴한 비용으로 활용할 수있었습니다. 그러나 최근 FPGA 회사의 초점은 데이터 센터 및 인공 지능 시장을 해결하기 위해 컴퓨팅 기능을 향상시키는 것이 었습니다. 이렇게 더 많은 컴퓨팅 요소를 추가하면 ATE 설계자에게 최소한의 또는 부정적인 이점으로 비용이 증가했습니다. 또한 ATE 시장에 서비스를 제공하는 구형 장치의 비용은 특히 대형 장치의 경우 급격히 증가하기 시작했습니다. 이로 인해 더 큰 FPGA를 사용하는 더 높은 채널 ATE의 비용이 FPGA에만 최대 $50 / 채널까지 증가했습니다.

200MHz 이상의 패턴 속도로 더 높은 성능의 ATE를 달성하기 위해 ATE 설계자는 맞춤형 또는 상용 형식 및 타이밍 발생기 IC를 사용해야합니다. 그런 다음 설계의 시퀀서 부분에 합리적인 비용의 FPGA를 사용할 수 있습니다.

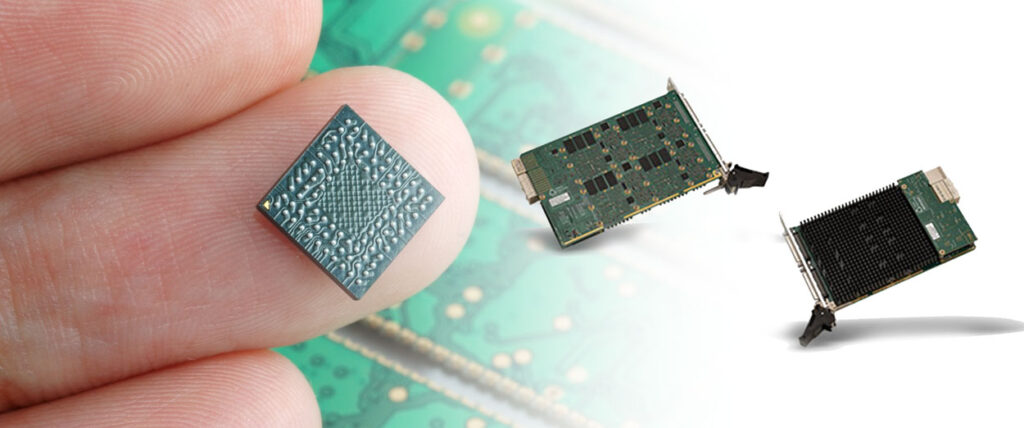

시판되는 타이밍 생성기는 소규모 ATE 회사에 디지털 ATE 계측의 성능 사다리를 마이그레이션 할 수 있도록합니다. 이 칩은 과도하게 제한되는 FPGA I / O없이 고성능 핀 드라이버에 인터페이스하도록 설계되었습니다.

하이 엔드 성능의 타이밍 칩을 구매하면 설계, 특성화 및 테스트 시간을 줄일 수있을뿐만 아니라 더 높은 성능의 디지털 ATE 사양을 제공하는 동시에 채널당 비용을 줄일 수 있습니다. 타이밍 정확도는 공급 업체에서 지정하며 시스템 테스트에서 이러한 매개 변수에 대한 광범위한 특성화 및 생산 테스트가 필요하지 않습니다.

상업용 타이밍 칩은 궁극적으로 에이티컴퍼니 개발 비용과 시장 출시 시간, 시스템의 전체 비용은 물론 더 높은 성능을 위한 경로를 제공합니다.