ATE Articles

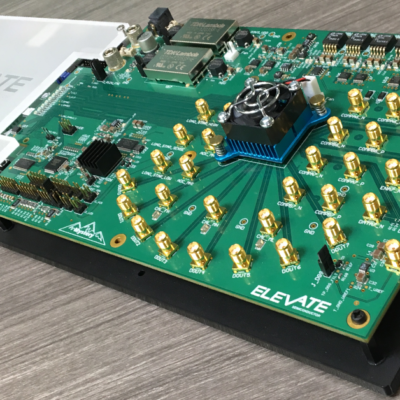

Elevate Semiconductor offers a diverse array of products, and the Evaluation Module (EVM) plays a pivotal role in the assessment…

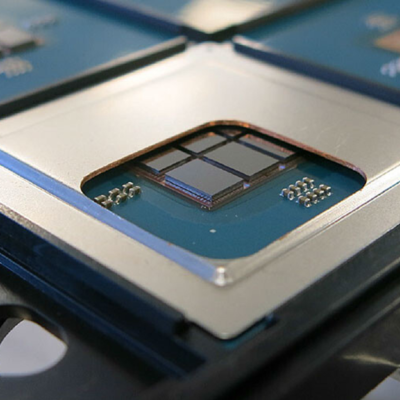

Tackling Complex Challenges in Semiconductor Chiplet Testing In semiconductor technology, chiplets have emerged as modular components that can operate either…

Interview with Anthony Turvey, Director of High Speed IC Design at ElevATE Interviewer: How did you end up in the…

AI Processors, such as prominent models like Graphcore and NVIDIA’s AI Super Chip GH200, demonstrate formidable computational power. With power…

By Simon Leigh, Elevate VP of Engineering As the intricacy of testing grows, it’s essential for ATE vendors to continually…

ACING THE TEST: THE CHIPS BEHIND THE CHIPS. ENGINEERING.COM The crucial ATE industry has never faced more challenges—but companies like…

ATE digital systems traditionally consist of sequencers, formatters, timing generators and pin electronics. The decision about which components to use for…

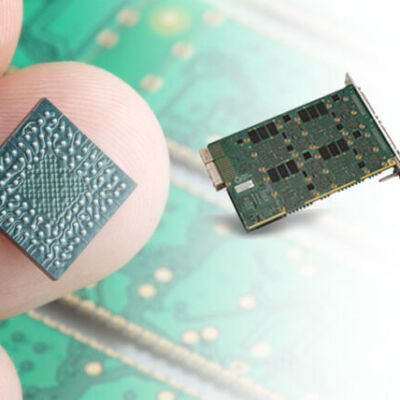

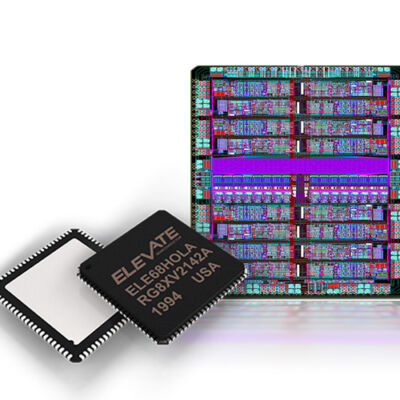

Typical integrated circuit (IC) solutions for pin electronics (PE) have been provided by multiple semiconductor companies in multiple different process…

MIPI Specifications and Testing ATE Articles / By admin The mobile industry processor interface (MIPI®) standard defines industry specifications for the design…

As technology evolves, and demand increases for next generation chips in artificial intelligence, deep learning, machine learning, automotive, IOT, healthcare…

Device Power Supplies (DPS) semiconductors provide flexible voltage and current force measurement capabilities to meet a wide range of test…

ELEVATE: WORLD LEADER IN INTEGRATED TEST TECHNOLOGY THE BASICS OF SEMICONDUCTOR TEST:Technology aficionados know Moore’s Law which states the number…